目前CPU用的内存正在从DDR2向DDR3过渡,而GPU用的显存则是以GDDR2/3为主、跳过GDDR4、直奔GDDR5而去。或许很多朋友一时还难以接受GDDR5那夸张的频率、不明白GDDR相比DDR发展速度为何如此“超前”、甚至搞不清楚GDDR1/2/3/4/5和DDR1/2/3之间“说不清道不明”的关系。

如果您是一位求知欲很强的电脑爱好者,那么本文非常适合您,笔者特意搜集了大量官方技术文档,为大家献上内存和显存鲜为人知的奥秘……

近年来CPU(中央处理器)和GPU(图形处理器)的发展速度之快让人目不暇接,新产品的运算能力成倍提升,此时就对内存子系统提出了严峻的需求,因为CPU/GPU运算所需的数据和生成的数据都是来自于内存/显存,如果存储速度跟不上,那么就会浪费很多时间在数据等待上面,从而影响CPU/GPU的性能发挥。

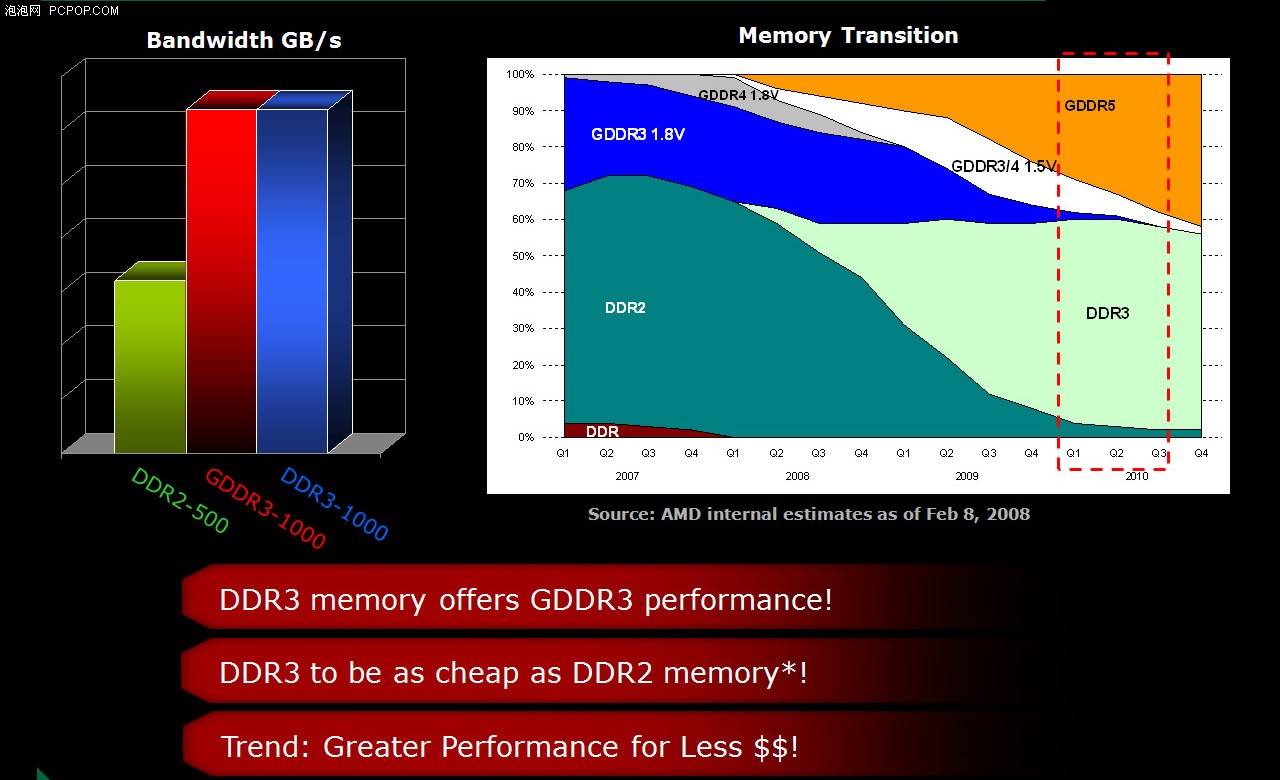

为了让内存/显存不至于造成瓶颈,芯片厂商都在想方设法的提高带宽:AMD和Intel相继将内存整合在了CPU内部,大大降低了延迟并提高存储效率,Intel旗舰级CPU能够支持三通道内存,带宽提升50%;ATI和NVIDIA也先后使用了512Bit的显存,总带宽倍增。

是何原因导致业界三大巨头如此大费周折呢?这是因为内存技术的发展速度,其实并不如大家想象中的那么快,受到很多技术难题和传统因素的制约,本文就对内存和显存的发展历程及相关技术进行详细分析。

为让评测文章更具参考价值,同时也让广大网友能够看到自己最感兴趣的内容,泡泡网DIY评测室特意开设了“You Think.I do”板块,您可以将最感兴趣的内容、甚至任何想法发送到邮箱“”,或加共同探讨,我们会有针对性地挑选网友关注的热点进行评测,一旦您的建议被采纳,我们会为您送出精美礼物一份!

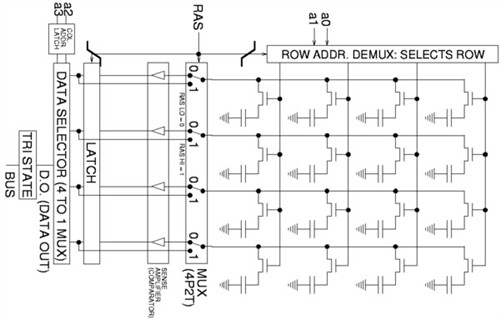

在半导体科技极为发达的省,内存和显存被统称为记忆体(Memory),全名是动态随机存取记忆体(Dynamic Random Access Memory,DRAM)。基本原理就是利用电容内存储电荷的多寡来代表0和1,这就是一个二进制位元(bit),内存的最小单位。

DRAM的结构可谓是简单高效,每一个bit只需要一个晶体管加一个电容。但是电容不可避免的存在漏电现象,如果电荷不足会导致数据出错,因此电容必须被周期性的刷新(预充电),这也是DRAM的一大特点。而且电容的充放电需要一个过程,刷新频率不可能无限提升(频障),这就导致DRAM的频率很容易达到上限,即便有先进工艺的支持也收效甚微。

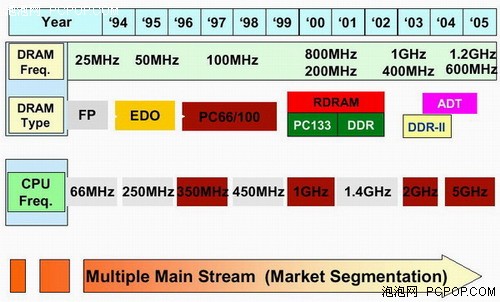

“上古”时代的FP/EDO内存,由于半导体工艺的限制,频率只有25MHz/50MHz,自SDR以后频率从66MHz一路飙升至133MHz,终于遇到了难以逾越的障碍。此后所诞生的DDR1/2/3系列,它们存储单元官方频率(JEDEC制定)始终在100MHz-200MHz之间徘徊,非官方(超频)频率也顶多在250MHz左右,很难突破300MHz。事实上高频内存的出错率很高、稳定性也得不到保证,除了超频跑简单测试外并无实际应用价值。

既然存储单元的频率(简称内核频率,也就是电容的刷新频率)不能无限提升,那么就只有在I/O(输入输出)方面做文章,通过改进I/O单元,这就诞生了DDR1/2/3、GDDR1/2/3/4/5等形形色色的内存种类,首先来详细介绍下DDR1/2/3之间的关系及特色。

通常大家所说的DDR-400、DDR2-800、DDR3-1600等,其实并非是内存的真正频率,而是业界约定俗成的等效频率,这些DDR1/2/3内存相当于老牌SDR内存运行在400MHz、800MHz、1600MHz时的带宽,因此频率看上去很夸张,其实线MHz而已!

内存有三种不同的频率指标,它们分别是核心频率、时钟频率和有效数据传输频率。核心频率即为内存Cell阵列(Memory Cell Array,即内部电容)的刷新频率,它是内存的真实运行频率;时钟频率即I/O Buffer(输入/输出缓冲)的传输频率;而有效数据传输频率就是指数据传送的频率(即等效频率)。

通过上表就能非常直观的看出,近年来内存的频率虽然在成倍增长,可实际上真正存储单元的频率一直在133MHz-200MHz之间徘徊,这是因为电容的刷新频率受制于制造工艺而很难取得突破。而每一代DDR的推出,都能够以较低的存储单元频率,实现更大的带宽,并且为将来频率和带宽的提升留下了一定的空间。

虽然存储单元的频率一直都没变,但内存颗粒的I/O频率却一直在增长,再加上DDR是双倍数据传输,因此内存的数据传输率可以达到核心频率的8倍之多!通过下面的示意图就能略知一二:

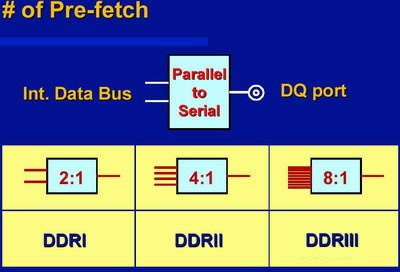

相信很多人都知道,DDR1/2/3内存最关键的技术就是分别采用了2/4/8bit数据预取技术(Prefetch),由此得以将带宽翻倍,与此同时I/O也必须做相应的改进。

预取,顾名思义就是预先/提前存取数据,也就是说在I/O发出请求之前,存储单元已经事先准备好了2/4/8bit数据。简单来说这就是把并行传输的数据转换为串行数据流,我们可以把它认为是存储单元内部的Raid/多通道技术,可以说是以电容矩阵为单位的。

这种存储阵列内部的实际位宽较大,但是数据输出位宽却比较小的设计,就是所谓的数据预取技术,它可以让内存的数据传输频率倍增。试想如果我们把一条细水管安装在粗水管之上,那么水流的喷射速度就会翻几倍。

明白了数据预取技术的原理之后,再来看看DDR1/2/3内存的定义,以及三种频率之间的关系,就豁然开朗了:

之所以被称为“同步”,因为SDR内存的存储单元频率、I/O频率及数据传输率都是相同的,比如经典的PC133,三种频率都是133MHz。

SDR在一个时钟周期内只能读/写一次,只在时钟上升期读/写数据,当同时需要读取和写入时,就得等待其中一个动作完成之后才能继续进行下一个动作。

双倍是指在一个时钟周期内传输两次数据,在时钟的上升期和下降期各传输一次数据(通过差分时钟技术实现),在存储阵列频率不变的情况下,数据传输率达到了SDR的两倍,此时就需要I/O从存储阵列中预取2bit数据,因此I/O的工作频率是存储阵列频率的两倍。

DQ频率和I/O频率是相同的,因为DQ在时钟上升和下降研能传输两次数据,也是两倍于存储阵列的频率。

DDR2在DDR1的基础上,数据预取位数从2bit扩充至4bit,此时上下行同时传输数据(双倍)已经满足不了4bit预取的要求,因此I/O频率必须加倍。

至此,在存储单元频率保持133-200MHz不变的情况下,DDR2的实际频率达到了266-400MHz,而(等效)数据传输率达到了533-800MHz。

DDR3就更容易理解了,数据预取位数再次翻倍到8bit,同理I/O频率也加倍。此时,在存储单元频率保持133-200MHz不变的情况下,DDR3的实际频率达到了533-800MHz,而(等效)数据传输率高达1066-1600MHz。

综上可以看出,DDR1/2/3的发展是围绕着数据预取而进行的,同时也给I/O造成了不小的压力,虽然存储单元的工作频率保持不变,但I/O频率以级数增长,我们可以看到DDR3的I/O频率已逼近1GHz大关,此时I/O频率成为了新的瓶颈,如果继续推出DDR4(注意不是GDDR4,两者完全不是同一概念,后文会有详细解释)的话,将会受到很多未知因素的制约,必须等待更先进的工艺或者新解决方案的出现才有可能延续DDR的生命。

前面介绍的是关于历代内存的技术原理,可以说是比较微观的东西,反映在宏观上,就是常见的内存颗粒及内存条了,这都是些看得见摸得着的东西,但有些概念还是不容易理解,这里一一进行说明:

内存模组的设计取决于内存(集成在北桥或者CPU内部),理论上位宽可以无限提升,但受制因素较多:高位宽将会让芯片组变得十分复杂,对主板布线提出严格要求,内存PCB更是丝毫马虎不得,内存颗粒及芯片设计也必须作相应的调整。可谓是牵一发而动全身,所以多年来业界都是墨守成规,维持64bit的设计不变。

相比之下,显卡作为一个整体就没有那么多的顾忌,只需重新设计GPU内部的显存,然后PCB按照位宽要求布线,焊更多的显存颗粒上去就行了,虽然成本也很高但实现512bit并没有太大难度。

既然实现高位宽内存条太难,那么就退而求其次,让两条内存并行传输数据,同样可以让位宽翻倍。目前流行的双通道技术就是如此,北桥或者CPU内部整合了两个独立的64bit内存,同时传输数据等效位宽就相当于128bit。

Intel Nehalem核心CPU直接整合三通道内存,位宽高达192bit。但由于CPU、主板、内存方面成本都增加不少,因此在主流Lynnfield核心CPU上面又回归了双通道设计。事实上服务器芯片组已经能够支持四通道内存,对服务器来说成本方面不是问题,只是对稳定性和容错性要求很高。

理论上,完全可以制造出一颗位宽为64bit的芯片来满足一条内存使用,但这种设计对技术要求很高,良品率很低导致成本无法控制,应用范围很窄。

所以内存芯片的位宽一般都很小,台式机内存颗粒的位宽最高仅16bit,常见的则是4/8bit。这样为了组成64bit内存的需要,至少需要4颗16bit的芯片、8颗8bit的芯片或者16颗4bit的芯片。

而显卡对位宽要求很高,容量反而退居其次,所以显存颗粒的位宽普遍比内存颗粒大(这就是显存和内存主要区别之一),比如GDDR3/4/5颗粒都是32bit,4颗就能满足低端卡128bit的需要,8颗可以满足高端卡256bit的需要;而低端GDDR2颗粒为16bit,需要8颗才能组成低端卡128bit的需要。

在芯片的内部,内存的数据是以bit为单位写入一张大的矩阵中,每个单元称为CELL阵列,只要指定一个行一个列,就可以准确地定位到某个CELL,这就是内存芯片寻址的基本原理。这个阵列我们就称为内存芯片的BAN。